53A-310 FET SCANNER MASTER CARD

ORDERING INFORMATION

53A-310 – FET Scanner Master Card

OPT 01 – User Prototype Area

OPT 1V – Add VXIbus Compatibility

53A-690 – Analog Cable

OPT 01 – One Slave

OPT 02 – Two Slaves

OPT 03 – Three Slaves

OPT 04 – Four Slaves

OPT 05 – Five Slaves

OPT 06 – Six Slaves

OPT 07 – Seven Slaves

53A-782 – Hooded Connector

• 32 differential analog channels

• Random channel selection

• Programmable scan rates up to 500,000 channels per second

• Analog input up to ±14V peak

• Optional wire-wrap area for user-developed input signal conditioning

• Controls up to seven 53A-311 FET Scanner Slave Cards for up to 256 input channels

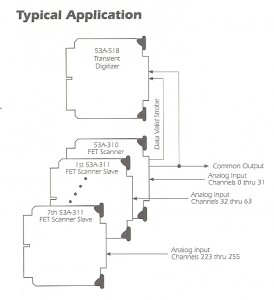

The 53A-310 FET Scanner Card is a thirty-two channel analog multiplexer for use in routing analog signals to measuring instruments, such as the 53A-522 Digital Multimeter or 53A-518 Transient Digitizer. The 53A-310 is capable of multiplexing up to 256 differential channels when used in conjunction with 53A-311 FET Scanner Slave Cards.

The dedicated microprocessor contained on the 53A-310 allows the 53A-310/311 scanner system to automatically execute a user programmed scanning sequence. The sequence can be made up of random or sequential channels, scanned in normal or reverse order. In addition, individual channels may be closed one at a time to ease system startup and troubleshooting. As with all CDS scanners, hardware interlocks automatically prevent more than one channel being closed at a time.

Using solid state switches. the 53A-310 is capable of accessing individual channels at a rate exceeding 500,000 channel selections per second. When automatic scanning is selected, the rate may be controlled by either the internal programmable scan rate generator or an external TTL input.

The 53A-310 is designed to interface to most types of measurement equipment. The Card can be used to generate the necessary timing and control signals for a complete data acquisition system, or it can respond to external control signals, as required. The scanner generates a data valid trigger each time a channel is closed. The sense of the trigger may be set by the user, allowing the 53A-310 Card to operate with instruments which trigger on either low-to-high or high-to-low transitions. In addition. the Card can be set to hold off the start of a scan sequence until an external trigger is received.

The common output of the scanner is available at both the front edge connector of the card and also at the rear connector for interfacing to the CDSbus System analog bus. The Card’s connection to the analog bus is under program control. In addition, connection to the analog system bus is switch-selectable to avoid possible bus use conflicts.

BITE

Built-In-Test Equipment (“BITE”) is provided by a series of front edge mounted LEDs that indicate if analog inputs are being scanned, when the Card has been programmed to use an external pace signal, or if the Card has detected a programming syntax error. The specific error condition detected can be returned to the system controller by means of the Error Report command.

Specifications

Number of Channels:

32 differential channels.

Channel Expansion:

Up to seven 53A-311 FET Scanner Slave Cards (total of 256 differential channels) can be controlled by a single 53A-310 Card.

Analog Signal Input Range:

±14V from either differential input to system common, including any common mode voltage.

Analog Bandwidth:

800 KHz (low impedance source. high impedance load).

Internal Scan Rate:

500 kHz maximum, programmable from 2 µsec to 16.772 sec in 1 µsec increments (6 decimal digits resolution).

Settling Time:

1.5 µsec to 12-bit accuracy.

Channel Resistance:

500 Ohms maximum each differential input line.

Channel Capacitance:

20 pF off. line to line.

200 pF on. line to line.

Off Isolation:

58 dB, at 800 KHz (50 Ohm source. 10 KOhm load).

Analog Input Current:

20 mA maximum.

Analog Input Protection:

Maximum Input Voltage (peak ac + dc). ±16.25 volts, either differential input to system common.

Data Valid Strobe Output

Logic Sense. switchable positive or negative edge. Delay programmable from 1 to 8 µsec after selection of new channel.

External Scan Input:

Logic Level, TTL fan out of 10 LSTTL loads.

External Trigger Input:

Logic Sense, switch-selectable. low-to-high or high-to-low transition. Logic Level, TTL, 1 LSTTL loads.

External Pace Input:

Logic Sense, positive edge triggered

Logic Level, TTL, 1 LSTTL load

Rate, DC to 800 KHz.

Digital Output (to 53A-311 FET Scanner Slave Cards):

TTL Levels, 8-bit parallel data bus providing channel address.

Programmed By:

ASCII Characters.

Required Cable(s):

53A-782 Hooded Connector or

53A-690 Analog Cable with 76-pin Hood Connector. When 53A-311 FET Scanner Slave Cards are used. order cable Option 01 through 07, corresponding to the number of slave cards used.

Two 53A-729 Adapter Cables (SMB Snap-on Plug to BNC Male) are required to access the Ext. Pace and Trigger inputs.

Available Options:

OPT 01, User prototype area on daughter board. Approximately 9 sq. in. available for user-designed input signal conditioning. Power Available. +5V dc (1.3A). ± 15V dc (150mA each).

OPT 1V, add VXIbus compatibility.