BIT ERROR RATE TESTING

The 53A-530 BERT and 53A-531 BERR FORMAT CONVERSION Cards are useful in applications which require programmable bit error rate testing. These applications include: Telecommunications Industry – testing the integrity of ground and satellite communications channels and equipment such as multiplexers, demultiplexers, digital radios, modems, etc.; Digital Computer Industry- testing magnetic tape drives, disc drives, etc.

The BERT and BERR Cards were designed to allow the user to, under program control, measure both “bit error’ and “peak block-error rate.” These measurements can be made irrespective of the transmission media path delay.

Under program control, the user can change the block size and introduce phase offset and phase jitter on the clock and data. Bit rates are programmable up to 10 Mb/s synchronous operation. Inputs are provided to allow the user to inject a specific number of errors into the system.

Eight programmable data formats are available:

NRZ, also known as “Polar NRZ and NRZ-L.”

RZ, also known as “Bipolar RZ.”

Alternate Mark Inversion (AMI), also known as “Bipolar.”

Diphase, also known as “Manchester.”

Conditioned NRZ, also known as “NRZ-M.”

Conditioned RZ.

Conditioned Bipolar:

Conditioned Diphase.

The wide range of formats and adjustable differential inputs and outputs ensure that the system will meet both present and future testing requirements without having to build external format conversion devices.

FORMAT CONVERSION

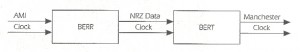

Since the BERT Card can receive NRZ data as well as transmit any format and the BERR Card can transmit NRZ data as well as receive any format the two cards connected as shown in the diagram below can be used to convert from one data format to another – e.g., AMI to Manchester:

**Note: Clock must be same frequency as data.

ERROR AND DISTORTION INJECTION

The diagram above can be used not only to reformat the data but also to programmatically distort (phase offset and jitter) the data and clock of a system. In addition, through inputs provided on the BERT Card. data errors may be injected into the data stream.

53A-531 BIT ERROR RATE RECEIVER (BERR) CARD

ORDERING INFORMATION

53A-531 – Bit Error Rate Receiver (BERR Card)

OPT 1V- Add VXIbus Compatibility

53A-780 – Hooded Connector

• Programmable input data format and input data pattern

• Programmable block size

• May be operated synchronous or asynchronous

• Synchronous data rates up to 10 Mb/s

• Asynchronous data rates up to 1.55 Mb/s

The Bit Error Rate Receiver Card (BERR) has a pseudo random binary sequence (PRBS) generator with the inverse transfer function of the PRBS on the 53A-530 BERT Card. Upon receiving fifteen bits of data from the BERT Card the BERR Card will attempt to synchronize with the incoming data. If synchronization is not achieved, 15 more bits will be examined and the process will repeat This feature allows the BERR Card to count data errors without regard to media path delay.

The BERR Card can be programmed to count errors within a block of data. The “block size” is programmable from 100 data bits to 900,000,000,000 bits. The “current bit error” counter retains the number of errors in the current block. The “peak block error rate” counter retains the peak number of errors counted in any block since the beginning of the test

There are two methods of receiving data (synchronous and asynchronous) which require two different methods of detecting data.

Synchronous Data Detection

The BERR Card will receive both data and clock from the unit under test (UUT), and will sample the data at the times indicated by the clock.

Asynchronous Data Detection

The BERR Card will receive only data from the UUT and will sample the data at times indicated by the last received data transition and the BERR’s programmed data rate. An example of asynchronous data might be recording data on digital magnetic tape from a BERT Card and later detecting the data with a BERR Card.

**Note: In this example there is no BERT Card or clock at the time the data is detected by the BERR.

BITE

A column of LEDs provides Built-In-Test Equipment (“BITE”) for the BERR Card. Two LEDs will blink when data is detected or the Card is synchronized with the data. Additional LEDs display the “peak block-error rate,” the current number of errors within the current block, the programmed block size and when the first block count is complete.

Specifications

Mode:

Receiver /Retransmitter.

Synchronous or Asynchronous.

This Card will retransmit with NRZ format all received data.

Types of Input Data Formats (programmable, conditioned or not):

NRZ.

RZ.

AMI (Bipolar).

Manchester.

Diphase.

Types of Data Patterns the Card Can Synchronize With (programmable):

PRBS.

Inverted PRBS.

(7, 9, 11 or 15 bit 2^n-1 sequence, switch-selectable).

Maximum Allowable Input Data Distortion for Automatic Synchronization:

Synchronous Data (NRZ), 18% distortion.

Asynchronous Data (NRZ), 18% distortion,

all other formats 9% distortion.

Data Source:

53A-530 BERT Card.

Data Block Size (programmable):

100 to 9 x 10^11 bits.

Maximum Current Block Error Count:

99 bit errors per block.

Maximum Peak Block Error Count:

99 bit errors per block.

Interrupts:

The BERR Card can cause a System interrupt on loss of synchronization to data, each “Error Hit” or first data block completed.

Oscillator BX Data Rate:

External, supplied by BERT Card or other user supplied frequency source.

Maximum Data Rates:

Synchronous. 10 Mb/s.

Asynchronous. 1.55 Mb/s.

Receivers for Input Data and Synchronous Input Data Clock:

Differential. (See 53A-530 Specifications.)

Drivers for Output Data and clock:

Single-ended TTL.

Programmed By:

ASCII Characters.

Recommended Cable:

53A-780.

Available Option:

OPT 1V. add VXIbus compatibility.